# A Novel Programmable Delay Line for VLSI Systems

Ankur Bal<sup>1</sup>, Jeet Narayan Tiwari<sup>1</sup>, Jai Narayan Tripathi<sup>1</sup>, Ramachandra Achar<sup>2</sup>

1: STMicroelectronics, Greater Noida, India; 2: Carleton University, Ottawa, Canada

## Agenda

- Motivation

- Contemporary Architecture

- Applications of Delay lines

- Proposed Novel Programmable Delay Architecture

- Simulation Results

- Key Benefits

- Conclusion

### **Motivation**

- In digital ASICs, controlled clock delay finds many applications.

- Several buffers are required for large absolute delays

- Along with accuracy, granular control is also desired

- Large buffers chains contribute to substantial Leakage power

- On chip Delay variation is seen among the delay elements

- The delay selection multiplexor has high fan-in

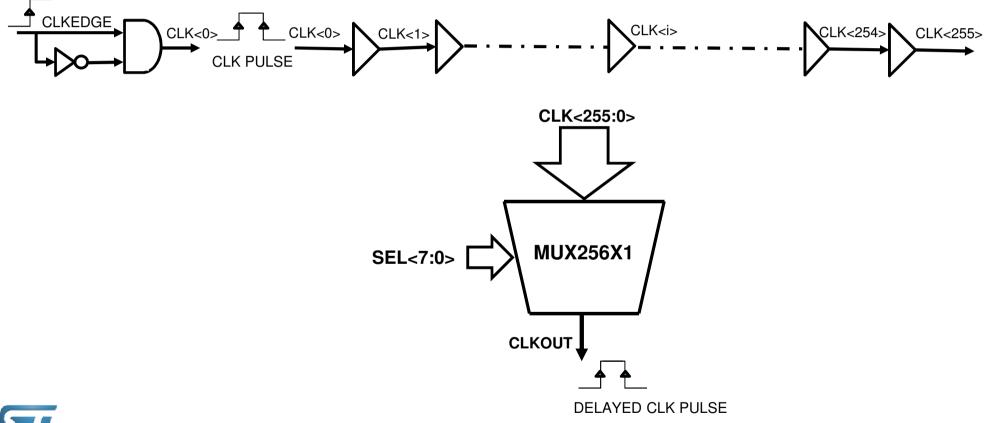

#### **Contemporary Architecture**

#### **Applications of Delay Lines**

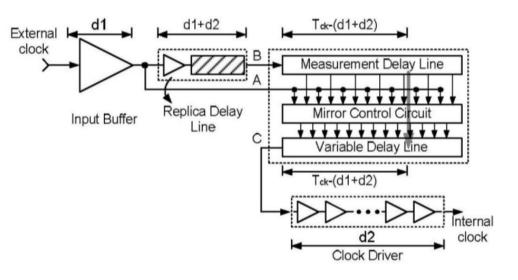

Synchronous Mirror Delay Circuit

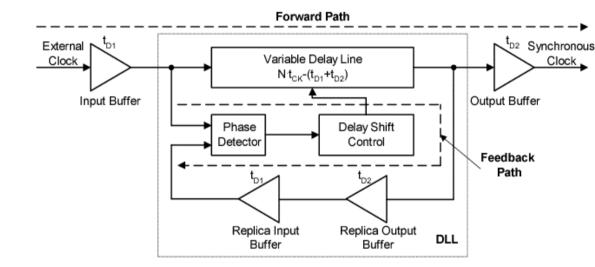

Delay Locked Loop

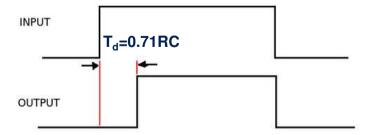

Clock-less, RC free, Delay

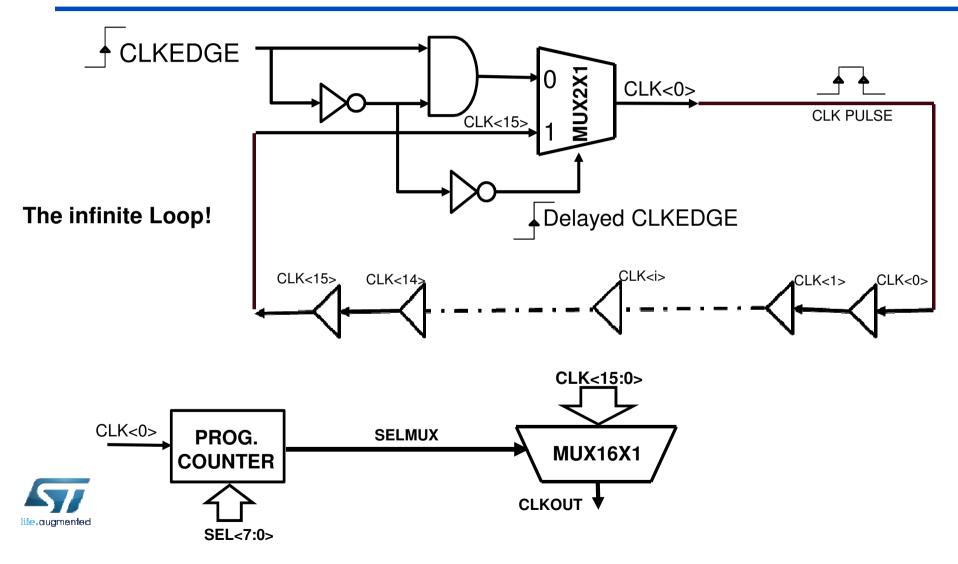

#### **Proposed Novel Programmable Delay Architecture**

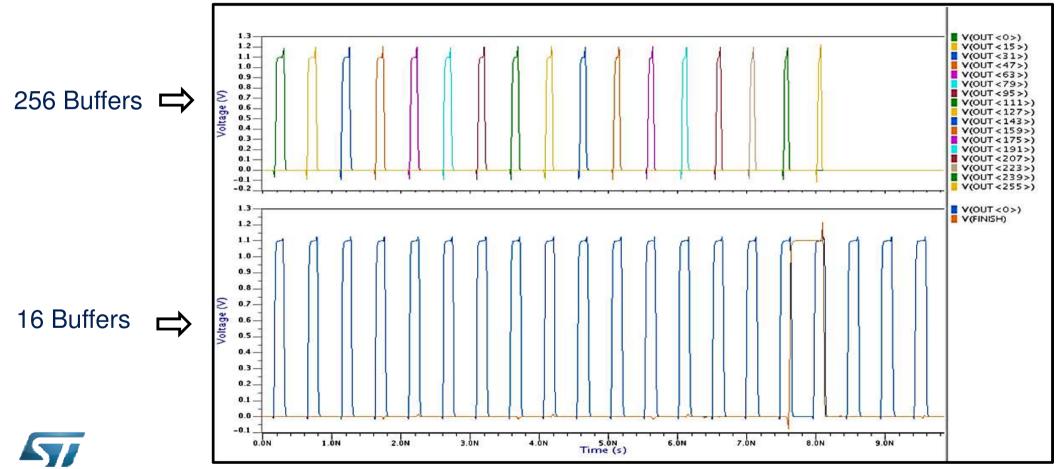

#### **Simulation Results: Delay Comparisons**

life.augmented

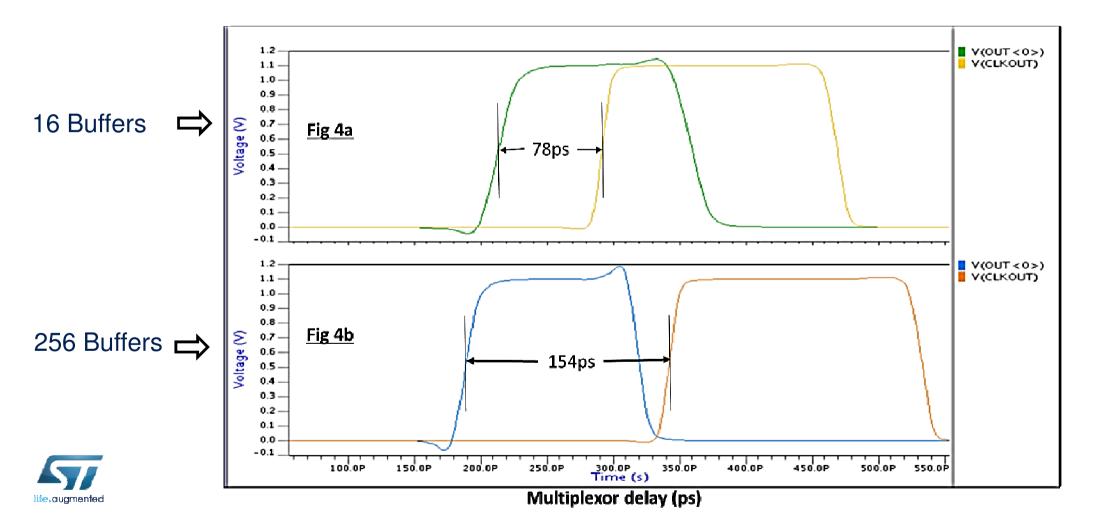

#### **Simulation Results: Selection Delays**

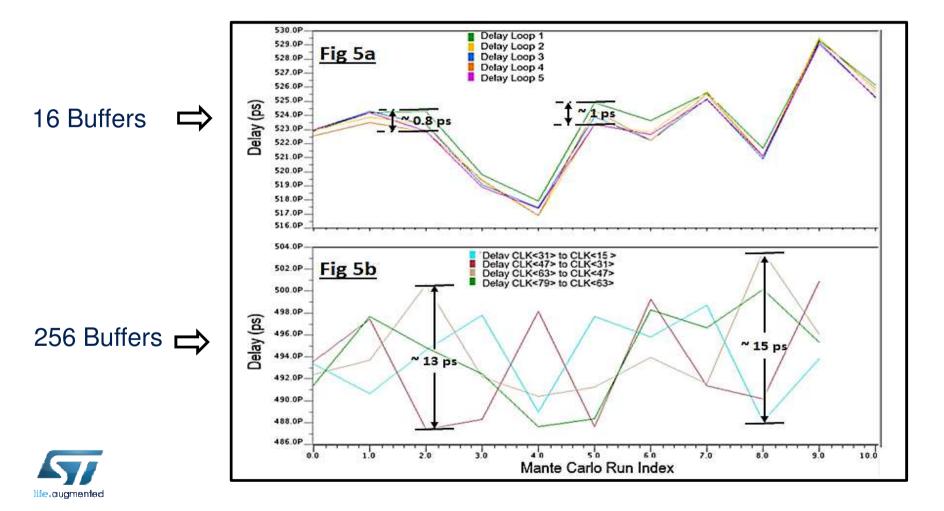

#### **Simulation Results: Delay Variation**

### Silicon Area Comparison

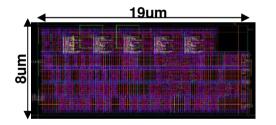

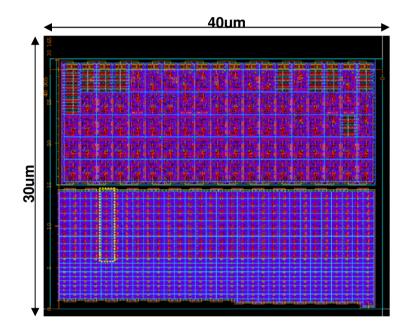

#### Area: 8X advantage

Proposed 256 buffer delay line:

• area = 19\*8 = 0.00152um2

Conventional 256 buffer delay line:

• area = 30\* 40 = 0.012um2

### Figure of Merit Comparison (in 28nm FDSOI)

|                            | Conventional | Proposed | Gain |

|----------------------------|--------------|----------|------|

| Area (in um <sup>2</sup> ) | 1200         | 150      | 8    |

| Leakage Power (in uA)      | 22.11        | 2.29     | 10   |

| MUX delay (in pS)          | 154          | 78       | 2    |

| Delay variation (in pS)    | 15           | 1        | 15   |

#### **Key Benefits**

- Use of lower number of buffers to achieve identical delay

- Low area and leakage power very useful in newer technologies

- Very low local variation across process corners

- Scalable to higher delays using minimal overheads

- Modular structure makes architecture implementation automable

- Plug and play usage in existing systems

#### Conclusion

- Design methodology for design of a programmable delay line circuit is presented

- A compact delay line circuit is demonstrated to generate multiple phases of clock

- A comparison of Figures-of-Merits with the conventional architecture reveals significant gain in terms of area, leakage power and variability

- This approach can be extended to arbitrary large delay generation by dynamic duty cycle correction

ankur.bal@st.com