# France Chambéry 18-21 june 2019

# SPI 2019

# 23<sup>RD</sup> IEEE WORKSHOP ON SIGNAL AND POWER INTEGRITY

IEEE CATALOG NUMBER: CFP19SPI-ART ISBN: 978-1-5386-8342-2 ©2019 IEEE

Dear colleagues and friends,

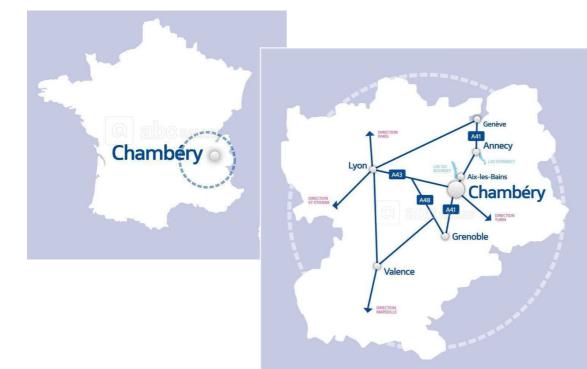

This is the second time I have the honor of serving as Chair of the IEEE Workshop on Signal and Power Integrity (SPI). The 23<sup>rd</sup> edition of SPI will be hosted by the magnificent city of Chambéry in the French Alps. The event is organized by the IMEP–LAHC laboratory and the Lab-STICC under the patronage of the Université de Savoie Mont Blanc, the Université de Bretagne Occidentale and the Ecole Nationale d'Ingénieurs de Brest.

SPI stays true to its reputation as a leading international conference in the field of Signal and Power Integrity. We are expecting participants from three continents. The program features a balanced selection of topics ranging from modeling to characterization and includes a special session titled "Emerging Substrate-Integrated Technologies" chaired by Dr. Anthony Ghiotto. The SPI Industry Forum is also back with a new edition organized and chaired by Dr. Aida Todri-Sanial.

This year's tutorial talks are exclusively dedicated to Si/Pi for automotive applications and are presented by engineers with first-hand experience of this emerging field – Yan Fen Shen and Ben Silva from the IoT Group, Intel Corporation and Stefanie Schatt from Continental Automotive.

We also have the privilege to welcome the co-founder of Kapteos, Dr. Gwenaël Gaborit who is this edition's Keynote Speaker.

Social events were carefully organized in the long standing tradition of the workshop. Participants will be able to discover the historic city of Chambéry, taste the exquisite local cuisine and enjoy the magnificent scenery of the French Alps.

I must express my gratitude to SPI authors; their work is the foundation of this conference. I am also grateful to the sponsors; the event would not be possible without their contribution. I was fortunate to have a reliable organization committee and I thank all the colleagues involved. The SPI Standing Committee has, as always, provided precious guidance and the Technical Program Committee was instrumental in selecting the papers. I thank them for their work.

I wish everyone an enjoyable and successful event and good fortune to future SPI organizers!

#### Mihai Telescu

SPI2019 General Chair

#### **WORKSHOP CHAIR**

#### Mihai Telescu

Université de Bretagne Occidentale, Brest (FRA)

#### **PROGRAM CO-CHAIRS**

Marc Le Roy Université de Bretagne Occidentale, Brest (FRA) Pascal Xavier Université Grenoble Alpes (FRA)

#### LOCAL ARRANGEMENTS CHAIR

#### **Grégory Houzet** Université de Savoie Mont-Blanc, Chambéry (FRA)

#### **STANDING COMMITTEE**

# Uwe Arz Physikalisch-Technische Bundesanstalt, Braunschweig (GER) Flavio G. Canavero Politecnico di Torino, Torino (ITA) Hartmut Grabinski Leibniz University Hannover, Hannover (GER) Stefano Grivet-Talocia Politecnico di Torino, Torino (ITA) Antonio Maffucci University of Cassino and Southern Lazio, Cassino (ITA) Michel S. Nakhla Carleton University, Ottawa (CAN) José E. Schutt-Ainé University of Illinois, Urbana-Champaign (USA)

Madhavan Swaminathan Georgia Institute of Technology, Atlanta (USA)

#### **INDUSTRY ADVISORY BOARD**

Stefano Grivet-Talocia (coordinator), Politecnico di Torino (ITA)

Kemal Aygun, Intel (USA)

Olivier Bayet, STMicroelectronics (FRA)

Hubert Harrer, IBM Boeblingen (GER)

Ivan Ndip, Fraunhofer IZM Berlin (GER)

Yutaka Uematsu, Hitachi (JAP)

#### **TECHNICAL PROGRAM COMMITTEE**

P. Aaen, Univ. Surrey (UK) R. Abhari, Santa Clara Univ. (USA) R. Achar, Univ. Carleton (CAN) G. Antonini, Univ. L'Aquila (ITA) W. Bandurski, Univ. Poznan (PL) D. Becker, IBM (USA) T. Dhaene, Ghent Univ. (BE) A. E. Engin, San Diego State Univ. (USA) J. Fan, Missouri, S&T Univ. (USA) F. Ferranti, IMT Atlantique (FRA) P. Franzon, NC State Univ. (USA) D. Gope, Indian Inst. Sci (IN) F. Grassi, Politech. Milano (ITA) E. Griese, Univ. Siegen (GER) **P. Gunupudi**, Univ. Carleton (CAN) **B. Gustavsen**, SINTEF (NO) J. Hejase, IBM (USA) **L. Jiang**, Univ. of Hong Kong (HK) D. G. Kam, Ajou Univ. (KR) T. Lacrevaz, Univ. Savoie (FRA) E. Liu, IHPC, A\*STAR (SG) Z. Mahmood, NanoSemi Inc. (USA)

I. Maio, Politech. Torino (ITA) P. Manfredi, Politech. Torino (ITA) K. L. Melde, Univ. Arizona (USA) **B. Nouri**, Univ. Carleton (CAN) **B. Ross**, Teraspeed Consulting (USA) S. Roy, Colorado State Univ. (USA) A. Ruehli, Missouri S&T Univ. (USA) **C. Schuster**, TU Hamburg-Harburg (GER) S. Shekhar, Intel (USA) **G. Signorini**, Intel (GER) I. Stievano, Politech. Torino (ITA) **N. Tanguy,** Univ Brest (FRA) **A. Todri-Sanial**, LIRMM (FRA) **R. Trinchero**, Politech. Torino (ITA) P. Triverio, Univ. Toronto (CAN) M. Tröscher, CST (GER) **D. Vande Ginste**, Ghent Univ. (BE) X. C. Wei, Zhejiang Univ. (CN) A. Weisshaar, Oregon State Univ. (USA) T. M. Winkel, IBM, Boeblingen (GER) T-L. Wu, Nat. Taiwan Univ. (TW) B. Xie, Intel (USA) W-Y. Yin, Zhejiang Univ. (CN)

#### LOCAL COMMITTEE

IMEP-LAHC, Université de Savoie Mont Blanc, Chambery (FRA)

Bernard Flechet Thierry Lacrevaz Grégory Houzet

#### IMEP-LAHC, Université Grenoble Alpes (FRA)

Pascal XAVIER (Program co-chair)

#### Lab-STICC, Université de Bretagne Occidentale, Brest (FRA)

Mihai Telescu (Workshop chair) Marc Le Roy (Program co-chair) Cédric Quendo (Treasurer) Noël Tanguy (Webmaster) Thierry LE Gouguec Pierre-Marie Martin

#### Lab-STICC, École Nationale d'Ingénieurs de Brest, Brest (FRA)

Laura Ghisa André Pérennou Stéphane Azou

#### Lab-STICC, Institut Mines-Télécom Atlantique, Brest (FRA)

Francesco Ferranti

# Tuesday June 18th

13:50 14:10 Tutorials Welcome

#### 14:10 15:30 Tutorials

#### **Power and Signal Integrity Challenges in IoT Automotive Applications**

#### Yan Fen Shen (IoT Group, Intel Corporation), Ben Silva (IoT Group, Intel Corporation)

The emergence of connected smart vehicles has fully transformed the in-vehicle experience, connecting drivers and technology, and will revolutionize the future of mobility. In this tutorial, we will discuss the latest trend in IoT automotive applications and the associated SoC+platform Signal Integrity (SI) & Power Integrity (PI) design challenges. Based on the desired level of vehicle autonomy and criticality of specific design features, electronics in the vehicle are categorized into different classifications/grades (AEC, ASIL, etc.) relative to capabilities, limitations, and functional safety. The end product dictates the use conditions that the vehicle's electronics must adhere to, including manufacturing, testing, thermal, and reliability. These use conditions can be much more stringent than standard consumer products and require diligent SI/PI engineering to work around these design challenges. At the same time, SI and PI performance enablers are in direct opposition to one another, so it becomes necessary to balance both disciplines and view the total system holistically to provide the best possible system performance. Examples of SI/PI challenges, tradeoffs, compromises, and simulation results will be presented.

**Yan Fen Shen** is a senior Power Integrity technical lead and project lead at Intel Corporation in the Internet of Things (IoT) Group. She has 17yrs of experience working in the field of Power Integrity, covering client computing and IoT products. Her interest and area of expertise are SoC+pl atform system level design and optimization, while pushing the envelopes of the latest technologies. She's also had firsthand experience working with end customers by conducting Power Integrity training classes, reviewing customer designs, and providing design guidelines. Her recent work

includes autonomous, computer vision, FIVR, and LPDDR5 developments.

**Ben Silva** is the technical lead and manager of the signal and power integrity team within the Internet of Things Group at Intel. He has been working in the field of signal and power integrity for almost 20 years with his current focus being system level signal/power integrity optimization and design. His past work focused on package level power integrity optimization, HSIO channel modeling/margin estimation, and full channel DDR modeling. His other interests include creating new signal/power integrity flows/methodologies to accelerate the product development cycle and simulation to lab correlation.

#### 15:30 16:10 Coffee break

#### 16:10 17:50 Tutorials

#### Autonomous driving as one of the key drivers for high speed design in automotive developments

#### **Stefanie Schatt (Continental Automotive)**

The development of advanced driver assistance systems especially for autonomously driving cars demands the integration of high speed interfaces to an extent previously unknown in automotive designs. The presentation will cover the specialties for signal and power integrity in today's automotive designs and give an overview over commonly used interfaces. One focus will also be the simulation sign-off of DDR4/LPDDR4/LPDDR4X interfaces which is specifically challenging due to the various constraints that are given by JEDEC, different vendors and technology.

**Stefanie Schatt** is an expert for high speed design simulation at Continental (Germany) with a strong focus on automotive applications. She provides specialized technical support in the field of signal integrity, power integrity and IRdrop on PCB level as well as 3D EMC simulations; she is involved in the development of flows and strategies to sign off complex designs. Before joining Continental, she worked for companies such as Cadence Design Systems and Infineon Technologies. She has 20 years of experience and a strong international background having worked with US and French-based engineering teams.

#### 18:15 Special tour and Welcome reception

### Wednesday June 19th

- 8:00 8:40 Welcome and Registration

- 8:40 9:20 Opening Session

- 9:20 10:20 Keynote speech

#### Optical sensing for the vectorial analysis of ultra-wideband electric field requirements, performances and applications

#### **Gwenaël Gaborit (Kapteos)**

The electric (E) field analysis is of major importance, and even mandatory, for many academic or industrial topics, such as energy monitoring, high voltage device contactless diagnostics, near field antenna characterization, bioelectromagnetism, electromagnetic compatibility, human exposure, military defence... Nevertheless, the exhaustive E-field measurement can be very complex due to the environment (very confined, presence of high magnetic field, near field configuration), to its intrinsic properties (e.g. close to or over the disruptive value, exotic polarization state, ultra-short pulse) or to societal/economic constraints. This keynote is focused on electro-optical (EO) sensing probes leading to a non-invasive and vectorial characterization of the E-field in environments and conditions not suitable for classical antennas. All the relevant characteristics leading to a comprehensive E-field measurement will be firstly defined and the EO effect will be explained. Then, a comparison with other widespread techniques (classical metallic transducers, bolometer, optoelectronic antennas...) will clarify strengths and limitations of this optical technique. The core of the presentation is dedicated to the experimental assessment of the field with several examples associated to the above identified applications. Measurement from quasi-DC up to terahertz region will be presented and analysed, for fields in guided or radiated configuration. Environments such as air, biological media or plasma are considered. I will also discuss the validity and the accuracy of absolute E-field measurements, depending obviously on the probe itself but also, dramatically, on the calibration procedure.

**Gwenaël Gaborit** was born in Lens, France, in 1978. He received the M.Sc. degree in Microwaves and Microelectronics from the University of Lille, France, in 2002. He received the Ph.D. Degree in Physics from the University of Savoie, France, in 2005. In 2005 he joined IMEP-LAHC laboratory as an associate professor. In 2009 he cofounded Kapteos and has been the company's Chief Science Officer ever since. He obtained his HDR (Habilitation à Diriger des Recherches) from the University Savoie-Mont-Blanc in 2014. His main research interests concern the development of electrooptic sensors dedicated to non-invasive electric field measurement. He is also involved in THz generation, detection and propagation.

#### Sponsor exhibition opens

#### 10:20 10:50 Poster exhibition / Coffee break

#### 10:50 12:10 Session 1 - Modeling and Design Flow for SI/PI (Chair: P. Manfredi)

10:50 - Performance Metrics for Crosstalk on Printed Circuit Boards in Frequency Domain - K. Scharff, H.-D. Bruns and C. Schuster - Institute of Electromagnetic Theory, Hamburg University of Technology, Hamburg, Germany

11:10 - Prediction of Frequency Dependent Shielding Behavior for Ground Via Fences in Printed Circuit Boards – T. Hillebrecht, D. Dahl and C. Schuster - Institute of Electromagnetic Theory, Hamburg University of Technology (TUHH), Hamburg, Germany

11:30 - Package Design Methodology for Crosstalk Mitigation between DC/DC Converter and ADC Analog Inputs in Complex SoC - F. Settino<sup>1,2</sup>, T. Brandtner<sup>1</sup>, J. Nieder<sup>1</sup>, F. Praemassing<sup>1</sup>, H. Koffler<sup>1</sup>, P. Palestri<sup>3</sup>, F. Crupi<sup>2</sup> - <sup>1</sup>Infineon Technologies Austria; <sup>2</sup>DIMES, University of Calabria, Italy; <sup>3</sup>DPIA, University of Udine, Italy

11:50 - A Novel Programmable Delay Line for VLSI Systems - A. Bal<sup>1</sup>, J.N. Tiwari<sup>1</sup>, J.N. Tripathi<sup>1</sup>, R. Achar<sup>2</sup> - <sup>1</sup>STMicroelectronics, Greater Noida, India; <sup>2</sup>Carleton University, Ottawa, Canada

#### 12:10 13:30 Lunch break

#### 13:30 13:50 Special session introduction

#### 13:50 15:30 Session 2 (Special) - Emerging Substrate Integrated Technology (Chair: A. Ghiotto)

13:50 - A Review of Compact Substrate Integrated Waveguide (SIW) Interconnects and Components - M. Bozzi<sup>1</sup>, L. Perregrini<sup>1</sup> and C. Tomassoni<sup>2</sup> - <sup>1</sup>Dept. of Electrical, Computer and Biomedical Engineering, University of Pavia, Italy; <sup>2</sup>Department of Engineering, University of Perugia, Italy

14:10 - Low Loss SISL Patch-Based Coupler with Arbitrary Coupling Coefficient - Y. Wang<sup>1</sup> and K. Ma<sup>2</sup> - <sup>1</sup>School of Physics, University of Electronic Science and Technology of China, Chengdu; <sup>2</sup>School of Microelectronics, Tianjin University, China

14:30 - Passive Opto-Antenna using Air-Filled Substrate-Integrated-Waveguide Technology – O. Caytan<sup>1</sup>, L. Bogaert<sup>1,2</sup>, H. Li<sup>1</sup>, J. Van Kerrebrouck<sup>1</sup>, S. Lemey<sup>1</sup>, J. Bauwelinck<sup>1</sup>, P. Demeester<sup>1</sup>, G. Torfs<sup>1</sup>, D. Vande Ginste<sup>1</sup> and H. Rogier<sup>1</sup> – <sup>1</sup>IDLab, Department of Information Technology, Ghent University; <sup>2</sup>Photonics Research Group, Department of Information Technology, Ghent University/imec

14:50 - Use of Multilayered-PCB for Q-band Substrate Integrated Waveguide Components – A. El Mostrah<sup>1</sup>, A. Manchec<sup>1</sup>, Y. Clavet<sup>1</sup>, and M. Cariou<sup>2</sup>, M. Sanchez-Soriano<sup>2</sup>, C. Quendo<sup>2</sup>, B. Potelon<sup>2</sup> - <sup>1</sup>Elliptika, Brest, France; <sup>2</sup>Univ Brest, Lab-STICC, CNRS, UMR 6285, Brest, France

15:10 - Recent Advances in Filter Design Using The AFSIW Technological Platform -T. Martin<sup>1,2,3</sup>, A. Ghiotto<sup>1</sup> and T.-P. Vuong<sup>3</sup> - <sup>1</sup>IMS, Univ. Bordeaux, France ; <sup>2</sup>Cobham Microwave, Cobham plc, Gradignan, France ; <sup>3</sup>IMEP-LAHC, Grenoble, France

#### 15:30 16:10 Session 3 - Stochastic / Sensitivity Analysis (Chair: D. Vande Ginste)

15:30 - A Hierarchical Approach to the Stochastic Analysis of Transmission Lines via Polynomial Chaos - P. Manfredi and R. Trinchero - Department of Electronics and Telecommunications, Politecnico di Torino, Italy

15:50 - Statistical Analysis of the Efficiency of an Integrated Voltage Regulator by means of a Machine Learning Model Coupled with Kriging Regression - R. Trinchero<sup>1</sup>, M. Larbi<sup>2</sup>, M. Swaminathan<sup>2</sup> and F. G. Canavero<sup>1</sup> - <sup>1</sup>EMC Group, Department of Electronics and Telecommunications, Politecnico di Torino, Italy; <sup>2</sup>School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, USA

#### 16:10 17:50 Poster Session (includes Coffee break) (Chair: O. Bayet)

- P1 CMOS Integrated PFM DC-DC Converter with Digitally-Controlled Frequency Selector -Junho Yu, Seungki Jeon, Hoyong Choi, and Namsoo Kim – School of ECE, Chungbuk National University, Cheong-ju, Korea

- P2 An Energy Efficient Spectrum Shaping Scheme for Substrate Integrated Waveguides -Yu Zhao, R. Grünheid, G. Bauch – Institute of Communications, Hamburg University of Technology, Germany

- P3 Via Transition Optimization Using a Domain Decomposition Approach A. Carmona-Cruz<sup>1</sup>, K. Scharff<sup>2</sup>, J. Cedeño-Chaves<sup>1</sup>, H-D. Brüns<sup>2</sup>, R. Rimolo-Donadio<sup>1</sup> and C. Schuster<sup>2</sup> - <sup>1</sup>Department of Electronics Engineering, Instituto Tecnologico de Costa Rica (ITCR), Cartago, Costa Rica; <sup>2</sup>Institut fur Theoretische Elektrotechnik, Technische Universitat, Hamburg-Harburg, Germany

- P4 Transmission Line Design for Testing High-Speed Integrated Circuits with Differential Signals – N. Bharat Thaker<sup>1</sup>, R. Ashok<sup>2</sup>, S. Manikandan<sup>2</sup>, N. Nambath<sup>3</sup>, S. Gupta<sup>2</sup> – <sup>1</sup>Silicon Photonics Product Division, Intel Technology India, Bengaluru, India; <sup>2</sup>Department of Electrical Engineering, IIT Bombay, Mumbay, India; <sup>3</sup>School of Electrical Sciences, IIT Goa, Ponda, India

- P5 Frequency-Domain Characterization of Power Inductors for Class-E Resonant Converters J. Bačmaga<sup>1</sup>, R. Blečić<sup>1</sup>, F. Pareschi <sup>2,3</sup>, R. Rovatti <sup>3,4</sup>, G. Setti <sup>2,3</sup>, A. Barić<sup>1</sup> <sup>1</sup>Department of Electronics and Telecommunications, Politecnico di Torino, Torino, Italy; <sup>2</sup>Advanced Research Center on Electronic Systems (ARCES), University of Bologna, Bologna, Italy; <sup>3</sup>Department of Electrical, Electronic and Information Engineering (DEI), University of Bologna, Bologna, Italy

- P6 A Method to predict Radiated Susceptibility of Printed Circuit Board from Near-Field Scan Immunity - A. Boyer – LAAS-CNRS, Univ Toulouse, France

- P7 Signal Quality Control for Cost-Effective Package Design Jisoo Hwang, Heeseok Lee, Hoi-Jin Lee and Youngmin Shin – Design Technology Team, System LSI Division, Samsung Electonics, Hwaseong-si, Korea

- P8 Modeling the Concentration Dependence for Manufacturing Single-Mode I/O Structures of MMI-Based Splitters in Thin Glass Sheets - J-P. Roth, T. Kühler and E. Griese – Theoretical Electrical Engineering and Photonics, University of Siegen, Germany

- P9 Open Defect Detection of Through Silicon Vias for Structural Power Integrity Test of 3D-Ics – K. Hachiya<sup>1</sup>, A. Kurokawa<sup>2</sup> - <sup>1</sup>Faculty of Modern Life, Teikyo Heisei University, Tokyo, Japan; <sup>2</sup>Graduate School of Science and Technology, Hirosaki University, Japan

- P10 Power integrity Flow for mixed-signal NVM flash IP X. Lecoq<sup>1</sup>, A. Lipani<sup>2</sup>, S. Stemmer<sup>1</sup>,

A. Chimeno<sup>3</sup> <sup>1</sup>STMicroelectronics Grenoble, MDG division, Grenoble, France;

<sup>2</sup>STMicroelectronics Palermo, MDG division, Palermo, Italy; <sup>3</sup>STMicroelectronics Crolles, TR&D division, Crolles, France

#### 18:15 Mountain and Lake Magic Tour

# Thursday June 20<sup>th</sup>

#### 8:00 8:40 Welcome and Registration

#### 8:40 10:20 Session 4 - Macromodeling and Model Order Reduction (Chair: S. Grivet-Talocia)

8:40 - On stabilization of parameterized macromodeling - A. Zanco, S. Grivet-Talocia, T. Bradde and M. De Stefano - Dept. Electronics and Telecommunications, Politecnico di Torino, Italy

9:00 - An IBIS-like Modelling for Power/Ground Noise Induced Jitter under Simultaneous Switching Outputs (SSO) - M. Souilem<sup>1,4</sup>, J. N. Tripathi<sup>2</sup>, W. Dghais<sup>3,4,5</sup> and H. Belgacem<sup>3,4</sup> - <sup>1</sup>Ecole Nationale d'Ingénieurs de Sousse, <sup>3</sup>Institut Supérieur des Sciences Appliquées et de Technologie, Université de Sousse, Tunisia; <sup>2</sup>STMicroelectronics Pvt. Ltd., Noida, India; <sup>4</sup>Laboratory of Elec. and Microelec. Université de Monastir, Tunisia; <sup>5</sup>Laboratoire d'Ingénierie des Systèmes Industriels et des Energies Renouvelables, ENSIT, Tunis

9:20 - A Bayesian Approach to Adaptive Frequency Sampling - S. De Ridder, D. Deschrijver, D. Spina, T. Dhaene and D. V. Ginste - IDLab, Department of Information Technology, Ghent University-imec, Belgium

9:40 - On the Extension of the TurboMOR-RC Reduction Method to RLC Circuits - F. Bekmambetova and P. Triverio - The Edward S. Rogers Sr. Department of Electrical and Computer Engineering, University of Toronto, Canada

10:00 - A Wide-Band Equivalent Circuit Model for Single Slot Defected Ground Structures - E. V. Nechel<sup>1</sup>, F. Ferranti<sup>2</sup>, Y. Rolain<sup>1</sup> and J. Lataire<sup>1</sup> – <sup>1</sup>Department of Fundamental Electricity and Instrumentation, Vrije Universiteit Brussel, Belgium; <sup>2</sup>Microwave Dept., IMT Atlantique, Lab-STICC, Brest, France

#### 10:20 10:50 Poster exhibition / Coffee break

#### 10:50 11:50 Session 5 - Electro-Magnetic Compatibility (Chair: P. Xavier)

10:50 - Finite element analysis of cable shields to investigate the behavior of the transfer impedance with respect to fast transients - S. Bauer<sup>1</sup>, C. Türk<sup>2</sup>, W. Renhart<sup>1</sup> and O. Bíró<sup>1</sup> - <sup>1</sup>Institute of Fundamentals and Theory in Electrical Engineering, Graz, Austria; <sup>2</sup>Ministry of Defence of Austria, Vienna, Austria

11:10 - Influence of Different Digital Power Supply Layout Styles on the EME of ICs with Respect to Process Variations - A. Rauchenecker and T. Ostermann - Dept. Energy Efficient Analog Circuits and Systems, Institute for Integrated Circuits, JKU University of Linz, Austria

11:30 - Study of the coupling of wide band Near Field Scan probe dedicated to the investigation of the radiated immunity of Printed Circuit Boards - A. Durier<sup>1,2</sup>, S. Ben Dhia<sup>2</sup> and T. Dubois<sup>3</sup> – <sup>1</sup>MEA- CMR, IRT Saint Exupery, Toulouse, France; <sup>2</sup>ESE, LAAS-CNRS / INSA Toulouse, France; <sup>3</sup>IMS Bordeaux, France

#### 11:50 12:30 Session 6 - Measurements and Characterization (Chair: M. Le Roy)

11:50 - A Method to Determine Wide Bandgap Power Devices Packaging Interconnections - L. Pace<sup>1,2</sup>, N. Defrance<sup>2</sup>, J-C. De Jaeger<sup>2</sup>, A. Videt<sup>1</sup> and N. Idir<sup>1</sup> -<sup>1</sup>Laboratory of Electrical Engineering and Power Electronics; <sup>2</sup>IEMN, University of Lille, France

12:10 - Turnkey Methodology for Characteristic Impedance Extraction of Embedded Transmission Lines - G. Houzet, P. Artillan, C. Bermond, T. Lacrevaz and B. Flechet – IMEP-LaHC, University Savoie Mont-Blanc, Le Bourget du Lac, France

#### 12:30 13:50 Lunch break

#### 13:50 15:10 Session 7 - Interconnect Design and Optimization (Chair: G. Houzet)

13:50 - Mode Conversion Due To Residual Via Stubs in Differential Signaling - J. Cedeno-Chaves<sup>1</sup>, K. Scharff<sup>2</sup>, A. Carmona-Cruz<sup>1</sup>, H.-D. Bruns<sup>2</sup>, R. Rimolo-Donadio<sup>1</sup> and C. Schuster<sup>2</sup> – <sup>1</sup>Department of Electronics Engineering, ITCR, Cartago, Costa Rica; <sup>2</sup>Institut für Theoretische Elektrotechnik, TUHH, Hamburg, Germany.

14:10 - Thermal and Signal Integrity Analysis of Novel 3D Crossbar Resistive Random Access Memories - F. Zayer<sup>1,2,3</sup>, K. Lahbacha<sup>1</sup>, W. Dghais<sup>1,3</sup>, H. Belgacem<sup>1,3</sup>, M. de Magistris<sup>4</sup>, A. V. Melnikovand<sup>5</sup>, A. Maffucci<sup>6,7</sup> - <sup>1</sup>Laboratory of Elec. and Microelec., <sup>2</sup>National Eng. School of Monastir, Tunisia; <sup>3</sup>Higher Inst. of Applied Science and Technology of Sousse, University of Sousse, Tunisia; <sup>4</sup>Dep. Electrical Eng. & Inform. Techn. University of Naples Federico II, Italy; <sup>5</sup>Institute for Nuclear Problems, Belarusian State University, Minsk, Belarus; <sup>6</sup>Dept of Electrical and Information Engineering, Univ. of Cassino and Southern Lazio, Italy; <sup>7</sup>INFN, Institute for Nuclear Physics, Frascati, Italy

14:30 - Analysis of Jitter for a Chain-of-Inverters including On-chip Interconnects - M. Suhail Illikkal<sup>1</sup>, J. N. Tripathi<sup>2</sup>, H. Shrimali<sup>1</sup> and R. Achar<sup>3</sup> – <sup>1</sup>School of Computing and Electrical Engineering, Indian Institute of Technology Mandi, India; <sup>2</sup>ST Microelectronics, Greater Noida, India; <sup>3</sup>Carleton University, Ottawa, Canada

14:50 - Optimization of a Miniaturized Ethernet 10 Gbits/s 8 Conductors Interconnect for Harsh Environments - Y. Boujmad<sup>1</sup>, P. Artillan<sup>1</sup>, C. Bermond<sup>1</sup>, O. Gavard<sup>2</sup>, M. Prudhom<sup>2</sup>, F. Khalili<sup>2</sup>, E. Husson-Charlet<sup>2</sup>, J.-P. Barbosa<sup>2</sup> and B. Flechet<sup>1</sup> - <sup>1</sup>IMEP-LaHC, Le Bourget du Lac, France; <sup>2</sup>Amphenol-Socapex, Thyez, France

#### 15:10 15:50 Poster exhibition / Coffee break

#### **Invited Talks:**

#### Trends and challenges of package electrical modeling in automotive context

#### Aurora Sanna (Back-End Manufacturing and Technology R&D, STMicroelectronics)

In the context of digital integrated circuits development, a growing focus on package electrical modeling is observed due to increasing operating frequencies, that make the impact of short interconnections potentially critical. In addition, package technology complexity is constantly evolving. Different platforms are available, each having its modeling challenges. Ball grid array (BGA) platform is now the standard for high-end automotive digital devices thanks to layout flexibility, that allows high interconnections density and multiple devices integration. Since many variables are involved, the electrical performance becomes strongly design-dependent and difficult to predict without accurate simulations. High density represents a challenge for simulation tools, that have to mesh very small details and provide accuracy combined to reasonable hardware requirements and runtime. A key aspect of package modeling is the strong link with design flow: simulation supports all the stages from pre-layout strategy definition to final post-layout validation. Following the trend to develop silicon, package and PCB in a co-design mode, a co-simulation approach is also needed: key aspects are tools automation, models standardization, data protection, parametric analysis. The automotive market has strict requirements in terms of electromagnetic emissions, leading to increasing interest in packagelevel shielding and decoupling techniques. The significant current density in advanced devices also puts the focus on electromigration effects and electro-thermal interaction, promoting a multiphysics approach.

**Aurora Sanna** got the master's degree in Electronic Engineering at Politecnico di Milano in 2011. She started working on electrical simulations at PCB level, focusing on electromagnetic emissions and then moving to power and signal integrity. She progressively extended her experience from PCB level to system level, including package and die effects. In 2017 she joined the BGA package development team at STMicroelectronics, inside Back-End Manufacturing and Technology R&D organization based in Agrate Brianza, Italy. She is now in charge of package level and

system level electrical modeling for package pre-layout and post-layout assessment. Her work is particularly focused on automotive products.

#### 3D-ADTCO: Architecture, Design and Technology Co-Optimization platform for High Energy Efficient 3D ICs

#### **Sébastien Thuries - CEA-LETI**

3D Technologies appear as a road to sidestep moore's law stagnation by providing high energy efficient vertical interconnect suitable interposer based computing system down to tight memory & logic integration . It is also suitable for heterogeneous compact integration required by smart sensors (AI). However, exploiting the third dimension raises many challenges in order to provide optimized 3D ICs, such as architecture partitioning, design methodology, technology reliability, while considering the cost of fabrication. In this talk, the speaker will present CEA-LETI's 3D architecture design and technology roadmap and associated co-optimization platform to optimize the power, performance,

area, and cost of M3D ICs. The speaker will introduce architecture breakthroughs possible thanks to High Density 3D (pitch < 1  $\mu$ m) and an overview of specific 3D ICs silicon prototypes CEA-LETI is currently designing and fabricating. He will present the 3D design tool box with a special focus on the digital design methodology, including process design kit add-on for place and route within fabrication cost guidelines, as well as 3D ICs thermal, power and signal integrity verifications. An overview of the 3D technology at device level including last pure MOSFET device status and its performance at low temperatures (CoolCubeTM), will also be exposed.

**Sébastien Thuries** is leading the High-Density 3D Architecture and Design group at CEA-LETI including fine pitch 3D Stacking as well as Monolithic 3D (M3D). He has worked on and led several Digital ASIC developments for a set of application like 4G Digital Base Band, Complex Imagers, System on Chip, Mixed Signal RF over the last decade...He has been a pioneer in FDSOI digital design and back biasing capability. He leads the research team on new architecture and design paradigm raised by M3D-IC in order to optimize the full system to technology fields. Sébastien Thuries has received his Master Degree in 2003 from Institut des Sciences de l'Ingénieur de

Montpellier (Poly'tech Montpellier) and joined CEA/Leti in 2004 as research engineer.

#### **Panel discussion**

**Sponsor exhibition closes**

18:15 Gala Dinner

# Friday June 21<sup>st</sup>

#### 8:00 9:00 Welcome and Registration

#### 9:00 10:20 Session 8 - Power Distribution Networks (Chair: M. Hashimoto)

9:00 - Understanding NAND AC Timing Parameters and How to Accurately Implement them in SI Simulation - S. Mobin and P. Balachander - Western Digital Corporation, Milpitas, CA, USA

9:20 - Power Delivery Network Pre-Layout Design Planning and Analysis Through Automated Scripting - C. M. Smutzer, C. K. White, C. R. Haider, and B. K. Gilbert - Mayo Clinic, Special Purpose Processor Development Group (SPPDG), Rochester, MN USA

9:40 - A Frequency-Dependent Target Impedance Method Fulfilling Both Average and Dynamic Voltage Drop Constraints - J. Chen, M. Hashimoto - Dept. Information Systems Eng., Osaka University, Japan

10:00 - Expert System Synthesis for Evolutionary Decoupling Capacitor Optimization -D. N. De Araujo and J. Pingenot - Electronic Board Systems Division, Mentor, a Siemens Business, USA

#### 10:20 10:50 Poster exhibition / Coffee break

# 10:50 11:50 Session 9 - Microwave and mmWave Solutions for SiP and SoC *(Chair: T. Lacrevaz)*

10:50 - RF line impedance optimization methodology in laminate technologies - T. Monnier<sup>1</sup>, S. Danaie<sup>2</sup> and L. Schwartz<sup>3</sup> – <sup>1</sup>ADL – Silicon Packaging; FMT – <sup>2</sup>EWS Services; Grenoble, <sup>3</sup>BEMT R&D – Central Packaging, STMicroelectronics, Grenoble, France

11:10 - Propagation Channel in Silicon in the Sub-THz Band for MPSoCs - I. El Masri, T. Le Gouguec and P.-M. Martin - Univ Brest, Lab-STICC, Brest, France

11:30 - Compact Analog All-Pass Phase-Shifter in 65-nm CMOS for 24/28 GHz on-Chipand in-Package Phased-Array Antenna - M. L. Carneiro<sup>1</sup>, M. Le Roy<sup>1</sup>, A. Pérennec<sup>1</sup>, R. Lababidi<sup>2</sup>, P. Ferrari<sup>3</sup> and V. Puyal<sup>4,5</sup> – <sup>1</sup>Univ Brest, Lab-STICC, Brest, France; <sup>2</sup>Ensta-Bretagne, Lab-STICC, Brest, France; <sup>3</sup>University of Grenoble Alpes, TIMA Laboratory, France; <sup>4</sup>University of Grenoble Alpes, Grenoble, France; <sup>5</sup>CEA, LETI, MINATEC campus, Grenoble, France

#### 11:50 12:30 Closing session

# Friday June 21st

# 22<sup>nd</sup> European IBIS Summit

| IBIS welcome reception, sign-in, refreshments                                                                                                                                                                                                                              |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Welcome and Introductions (M. Schaeder, Zuken, Germany)                                                                                                                                                                                                                    |  |  |  |

| IBIS Chair's Report<br>R. Wolff, Micron Technology, USA                                                                                                                                                                                                                    |  |  |  |

| Addressing Non-Ideal TX-FFE Behavior of High-Speed Drivers through<br>Hierarchical Waveform Approximations<br>C. Siviero, R. Trinchero, S. Grivet-Talocia, I. Stievano, T. Bradde, Politecnico di<br>Torino, Italy; M. Telescu, Université de Bretagne Occidentale, France |  |  |  |

| An Adaptive Algorithm for Fully Automated Extraction of Passive Parameterized<br>Macromodels<br>A. Zanco, E. Fevola, S. Grivet-Talocia, T. Bradde, M. De Stefano, Politecnico di<br>Torino, Italy                                                                          |  |  |  |

| Break, refreshments                                                                                                                                                                                                                                                        |  |  |  |

| Introducing IBIS Version 7.0<br>M. Mirmak, Intel Corporation, USA                                                                                                                                                                                                          |  |  |  |

| IBIS File Format Links<br>B. Ross, Teraspeed Labs, USA                                                                                                                                                                                                                     |  |  |  |

| Open discussion                                                                                                                                                                                                                                                            |  |  |  |

| Closing remarks (M. Schaeder, Zuken, Germany)                                                                                                                                                                                                                              |  |  |  |

| End of meeting                                                                                                                                                                                                                                                             |  |  |  |

|                                                                                                                                                                                                                                                                            |  |  |  |

# **SOCIAL EVENTS**

#### WELCOME RECEPTION - Tuesday June 18th

**Welcome reception at the convention center "Le manège"**. A rich buffet was selected including local specialties.

Chambéry is not only a popular destination for mountaineers but also a city with a very rich history. A visit of the ducal castle in Chambéry is scheduled before the traditional Welcome Reception.

#### Mountain and Lake Magic Tour - Wednesday June 19th

Participants will have the opportunity to discover the Mountains near Chambéry and dine on the shores of the Bourget Lake.

#### GALA DINNER - Thursday June 20<sup>th</sup>

**The Gala Dinner will take place at the Domaines des Saints Pères** where participants will discover the exquisite cuisine of the Savoy region and enjoy a magnificent view of the French Alps

The 23<sup>rd</sup> IEEE Workshop on SPI will be hosted in the Convention Center "Le Manège", downtown Chambéry

Le Manège 331 Rue de la République, 73000 Chambéry, France

| SPI 2 | 2019  | Tuesday June 18 <sup>th</sup>                                                                                                                      | Wednesday June 19 <sup>th</sup>                      | Thursday June 20 <sup>th</sup>             | Friday June 21 <sup>st</sup>                      | SPI 2 | 019   |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------|---------------------------------------------------|-------|-------|

| 08:00 | 08:20 |                                                                                                                                                    | SPI 2019<br>Welcome and Registration                 | SPI 2019                                   |                                                   | 08:00 | 08:20 |

| 08:20 | 08:40 |                                                                                                                                                    |                                                      | Welcome and Registration                   | SPI 2019<br>Welcome and Registration              | 08:20 | 08:40 |

| 08:40 | 09:00 |                                                                                                                                                    | Onoming Coosier                                      |                                            |                                                   | 08:40 | 09:00 |

| 09:00 | 09:20 |                                                                                                                                                    | Openning Session                                     | Session 4                                  |                                                   | 09:00 | 09:20 |

| 09:20 | 09:40 |                                                                                                                                                    | Keynote                                              | Macromodeling and<br>Model Order Reduction | Session 8                                         | 09:20 | 09:40 |

| 09:40 | 10:00 |                                                                                                                                                    | Optical sensing for the vectorial analysis of ultra- | Model Order Reduction                      | Power Distribution Networks                       | 09:40 | 10:00 |

| 10:00 | 10:20 |                                                                                                                                                    | wideband electric field<br>G. Gaborit (Kapteos)      |                                            |                                                   | 10:00 | 10:20 |

| 10:20 | 10:50 |                                                                                                                                                    | Poster exhibition<br>Coffee break                    | Poster exhibition<br>Coffee break          | Poster exhibition<br>Coffee break                 | 10:20 | 10:50 |

| 10:50 | 11:10 |                                                                                                                                                    |                                                      | Session 5                                  | Session 9                                         | 10:50 | 11:10 |

| 11:10 | 11:30 |                                                                                                                                                    | Session 1<br>Modeling and Design                     | Electro-Magnetic<br>Compatibility          | Microwave and mmWave<br>Solutions for SiP and SoC | 11:10 | 11:30 |

| 11:30 | 11:50 |                                                                                                                                                    | Flow for SI/PI                                       | Compatibility                              | Solutions for SiP and Soc                         | 11:30 | 11:50 |

| 11:50 | 12:10 |                                                                                                                                                    |                                                      | Session 6<br>Measurements and              | Closing Session                                   | 11:50 | 12:10 |

| 12:10 | 12:30 |                                                                                                                                                    |                                                      | Characterization                           | Closing Jession                                   | 12:10 | 12:30 |

| 12:30 | 12:50 |                                                                                                                                                    | Lunch break                                          |                                            |                                                   | 12:30 | 12:50 |

| 12:50 | 13:10 |                                                                                                                                                    | Lunch Dieak                                          | Lunch break                                | IBIS welcome Reception                            | 12:50 | 13:10 |

| 13:10 | 13:30 |                                                                                                                                                    |                                                      | Lunch break                                |                                                   | 13:10 | 13:30 |

| 13:30 | 13:50 |                                                                                                                                                    | Special session introduction                         |                                            |                                                   | 13:30 | 13:50 |

| 13:50 | 14:10 | Tutorials Welcome                                                                                                                                  |                                                      |                                            |                                                   | 13:50 | 14:10 |

| 14:10 | 14:30 | Tutorial                                                                                                                                           | Session 2 (Special)                                  | Session 7<br>Interconnect Design and       |                                                   | 14:10 | 14:30 |

| 14:30 | 14:50 | Power and Signal Integrity<br>Challenges in IoT                                                                                                    | Emerging Substrate<br>Integrated Technology          | Optimization                               |                                                   | 14:30 | 14:50 |

| 14:50 | 15:10 | Automotive Applications Yan<br>Fen Shen & Benjamin Silva                                                                                           | integrated recimology                                |                                            |                                                   | 14:50 | 15:10 |

| 15:10 | 15:30 | (Intel)                                                                                                                                            |                                                      | Poster exhibition                          | IBIS European Summit                              | 15:10 | 15:30 |

| 15:30 | 15:50 | Coffee break                                                                                                                                       | Session 3<br>Stochastic / Sensitivity                | Coffee break                               |                                                   | 15:30 | 15:50 |

| 15:50 | 16:10 |                                                                                                                                                    | Analysis                                             |                                            |                                                   | 15:50 | 16:10 |

| 16:10 | 16:30 | Tutorial<br>Autonomous driving as one<br>of the key drivers for high<br>speed design in automotive<br>developments Stefanie<br>Schatt (Contiental) |                                                      |                                            |                                                   | 16:10 | 16:30 |

| 16:30 | 16:50 |                                                                                                                                                    |                                                      | Interactive Industry Forum                 |                                                   | 16:30 | 16:50 |

| 16:50 | 17:10 |                                                                                                                                                    | Poster Session<br>(includes Coffee break)            |                                            |                                                   | 16:50 | 17:10 |

| 17:10 | 17:30 |                                                                                                                                                    |                                                      |                                            |                                                   | 17:10 | 17:30 |

| 17:30 | 17:50 |                                                                                                                                                    |                                                      |                                            |                                                   | 17:30 | 17:50 |

| SPI 2019<br>From 17: 00,Welcome and<br>Registration       | Social entertainment                             | Social entertainment          |

|-----------------------------------------------------------|--------------------------------------------------|-------------------------------|

| 18:15 - 22:00<br>Special Tour<br>and<br>Welcome reception | 18:15 - 21:30<br>Mountain and Lake<br>Magic Tour | 18:15 - 23:30<br>Social Event |