# Analysis of Jitter for a Chain-of-Inverters including On-chip Interconnects

M. S. Illikkal<sup>1</sup>, J N. Tripathi<sup>2</sup>, H. Shrimali<sup>1</sup>, R. Achar<sup>3</sup>

Indian Institute of Technology Mandi, INDIA

STMicroelectronics, INDIA

Carleton University, Canada

## Outline

- Introduction

- Power Supply Induced Jitter (PSIJ)

- Semi-analytical Modeling: EMPSIJ

- Chain-of-Inverters with interconnects

- Results

#### Introduction

- Low power, smaller area, higher switching frequencies.

- Leads to voltage fluctuations in PDNs.

- IR-drop, Ldi/dt noise, LC resonance, Crosstalk, Electromagnetic interference.

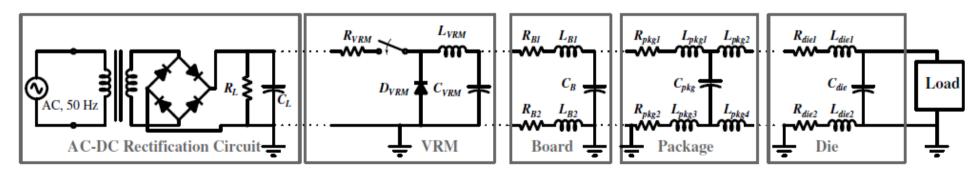

A typical Power Distribution Network (PDN)

#### **Jitter**

- Low power, smaller area, higher switching frequencies.

- Can be categorized in Random Jitter (RJ) and Deterministic Jitter (DJ).

- DJ → Inter-symbol Interference (ISI), Simultaneous Switching Noise (SSN), Ground Bounce, EMI, etc.

- Jitter budgets are defined to maintain timing margins.

## **Power Supply Induced Jitter**

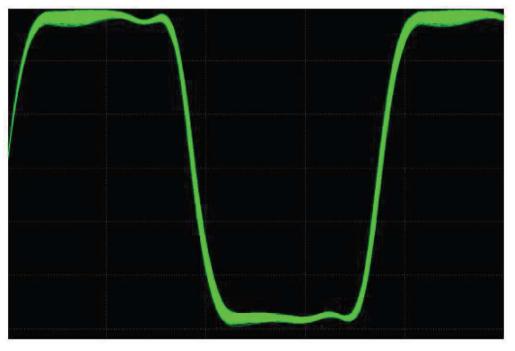

#### Worst Case PVT SS-40

Period Jitter: -16.1ps/6.3ps

Period Jitter: -91.6ps/110.9ps

#### Worst Case PVT SS-40

5

#### **Recent Work**

- Slope based Approaches

- J. Kim et al., IEEE EMC Symp., Aug. 2011.

- J. N. Tripathi et al., EMPSIJ, T-CPMT, Oct. 2017.

- Delay-based Approaches

- X. J. Wang and T. Kwasniewski, TEMC, Apr. 2016.

- J. N. Tripathi et al., TVLSI, Oct. 2017.

- Statistical methods:

- J. Kim et al., IEEE TCAS-1, Jul. 2014.

- Via IBIS Models

- X. Chu et al., TEMC, Nov. 2017.

- Numerical Method

- J. N. Tripathi and F. Canavero, IEEE MWCL, Dec. 2017.

- Efficient Modeling of Power Supply Induced Jitter (EMPSIJ). → TCPMT, Oct. 2017.

- Slope based Semi-analytical approach.

- Requires only one-bit simulation to evaluate the slope (β).

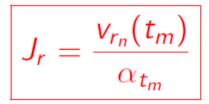

- TIE for k<sup>th</sup> bit can be calculated as:

$$\Gamma \mathrm{IE}^k = J_r^k = \frac{(v_{r_n}^k)_{t_m}}{\beta}$$

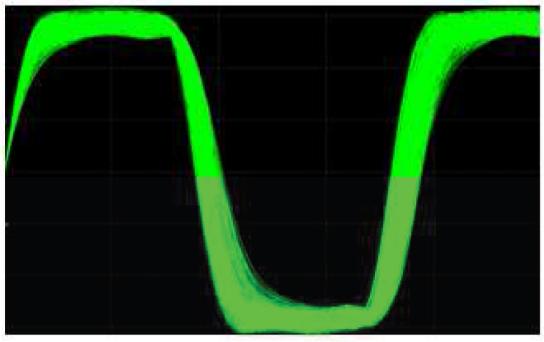

## **Power Supply Noise in a CMOS Inverter**

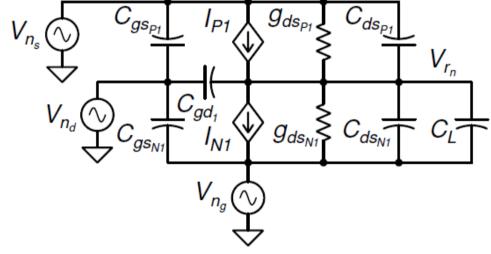

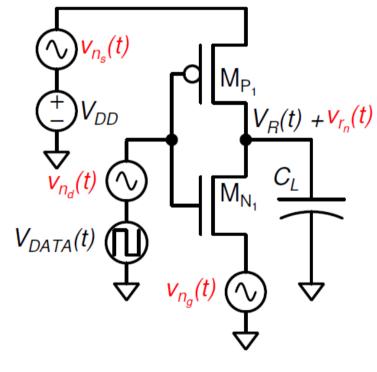

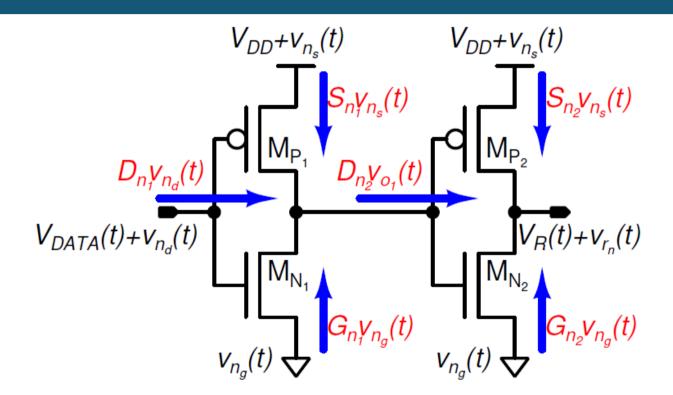

- $S_n$ ,  $G_n$ , and  $D_n$  are the transfer functions of respective paths.

- $v_{ns}(t)$ ,  $v_{ng}(t)$  and  $v_{nd}(t)$  are input noise components.

- $v_{DATA}(t)$  and  $v_R(t)$  are the input and output data signals.

- $v_{rn}(t)$  is the total output noise.

$V_{DD}+V_{n_s}(t)$   $V_{DATA}(t)+V_{n_d}(t)$   $V_{n_d}(t)$   $V_{n_d}(t)$   $V_{n_d}(t)$   $V_{n_d}(t)$   $V_{n_g}(t)$   $V_{n_g}(t)$

8

**PSN Components and their paths in CMOS inverter.**

### **PSN Components**

The total output noise,

$$v_{r_n}(t) = v_{r_s}(t) + v_{r_g}(t) + v_{r_d}(t)$$

Where,

$$v_{r_s}(t) = S_n v_{n_s}(t)$$

$v_{r_g}(t) = G_n v_{n_g}(t)$

$v_{r_d}(t) = D_n v_{n_d}(t)$

9

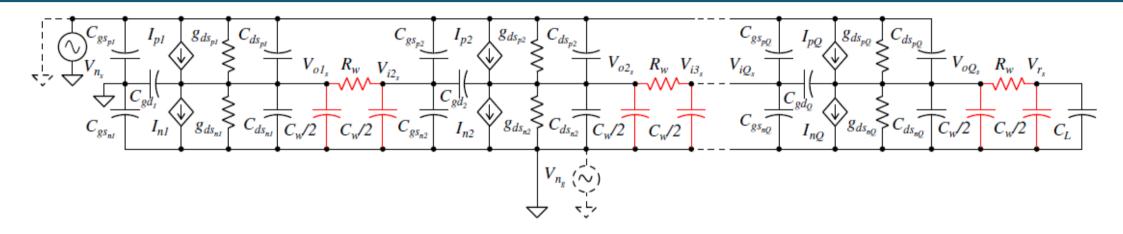

### Large Signal Analysis and Small-signal Model

10

lite.auamented

#### **Noise Transfer Functions**

$$S_{n} = \frac{V_{r_{s}}}{V_{n_{s}}} = \frac{g_{ds_{P}} + g_{m_{P}}}{g_{ds_{P}} + g_{ds_{N}} + j\omega_{s}(C_{gd} + C_{ds_{P}} + C_{ds_{N}} + C_{L})}$$

$$G_{n} = \frac{V_{r_{g}}}{V_{n_{g}}} = \frac{g_{ds_{N}} + g_{m_{N}}}{g_{ds_{P}} + g_{ds_{N}} + j\omega_{g}(C_{gd} + C_{ds_{P}} + C_{ds_{N}} + C_{L})}$$

$$D_{n} = \frac{V_{r_{d}}}{V_{n_{d}}} = \frac{j\omega_{d}C_{gd} - g_{m_{P}} - g_{m_{N}}}{g_{ds_{P}} + g_{ds_{N}} + j\omega_{d}(C_{gd} + C_{ds_{P}} + C_{ds_{N}} + C_{L})}$$

Small-signal model in frequency domain.

#### **Noise Transfer Functions**

Inverter with noise sources.

#### Input noise

$$v_{n_s}(t) = A_s \sin(2\pi f_s t + \phi_s)$$

$$v_{n_d}(t) = A_d \sin(2\pi f_d t + \phi_d)$$

$$v_{n_g}(t) = A_g \sin(2\pi f_g t + \phi_g)$$

Output noise

$$v_{r_s}(t) = |S_n| A_s \sin(2\pi f_s t + \phi_s + \angle S_n)$$

$$v_{r_g}(t) = |G_n| A_g \sin(2\pi f_g t + \phi_g + \angle G_n)$$

$$v_{r_d}(t) = |D_n| A_d \sin(2\pi f_d t + \phi_d + \angle D_n)$$

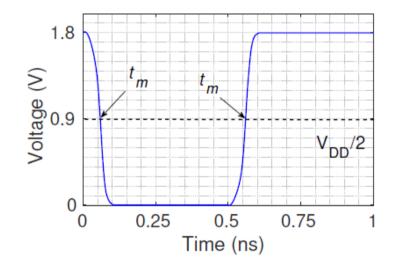

#### **Estimation of TIE and PSIJ**

$$v_{r_n}(t_m) = v_{r_s}(t_m) + v_{r_g}(t_m) + v_{r_d}(t_m)$$

$v_{r_n}(t_m)$  - Noise amplitude at  $t_m$

$\alpha_{t_m}$  - Slope at  $t_m$

$$J_{PP} = \frac{max[v_{r_n}(t_m)] - min[v_{r_n}(t_m)]}{\alpha_{t_m}}$$

#### **PSN in Chain of Inverters**

PSN Components and their paths in two cascaded inverters.

14

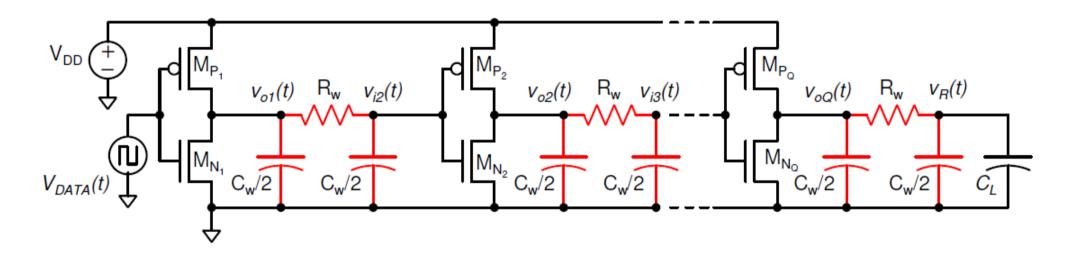

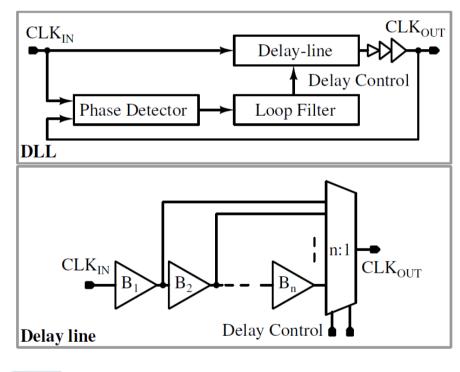

#### **Chain of Inverters with Interconnect**

15

**Chain of Inverters with On-Chip Interconnects**

#### **Noise Transfer Functions**

$$d_{1_s}V_{o1_s} + u_{1_s}V_{i2_s} = b_{1_s}V_{n_s}$$

$$l_{2_s}V_{o1_s} + d_{2_s}V_{i2_s} + u_{2_s}V_{o2_s} = b_{2_s}V_{n_s}$$

:

$$I_{(2Q)_{s}}V_{(oQ)_{s}}+d_{(2Q)_{s}}V_{r_{n}}=b_{(2Q)_{s}}V_{n_{s}}$$

#### **Noise Transfer Functions**

•

$$\mathbf{X}_{s}(j\omega_{s}) = \mathbf{A}_{s}(j\omega_{s})^{-1}\mathbf{B}_{s}(j\omega_{s})V_{n_{s}}(j\omega_{s})$$

•

$$\mathbf{X}_g(j\omega_g) = \mathbf{A}_g(j\omega_s)^{-1} \mathbf{B}_g(j\omega_s) V_{n_g}(j\omega_g)$$

#### where,

$$\mathbf{X}_{s}(j\omega_{s}) = \begin{bmatrix} V_{o1_{s}}(j\omega_{s}) \\ V_{o2_{s}}(j\omega_{s}) \\ \vdots \\ V_{o(2Q-1)_{s}}(j\omega_{s}) \end{bmatrix}; \ \mathbf{B}_{s}(j\omega_{s}) = \begin{bmatrix} b_{1_{s}}(j\omega_{s}) \\ b_{2_{s}}(j\omega_{s}) \\ \vdots \\ b_{(2Q-1)_{s}}(j\omega_{s}) \\ b_{2Q_{s}}(j\omega_{s}) \end{bmatrix}$$

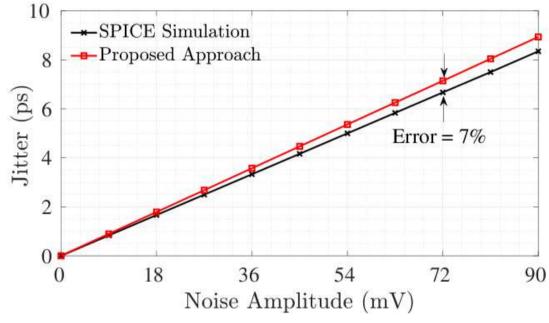

#### **Results**

#### **Ex-1: Chain of inverters with 5 stages**

| Technology used | BiCMOS 55nm (STMicroelectronics) |

|-----------------|----------------------------------|

| Supply voltage  | 1.8 V                            |

| Input data rate | 2 Gbps                           |

18

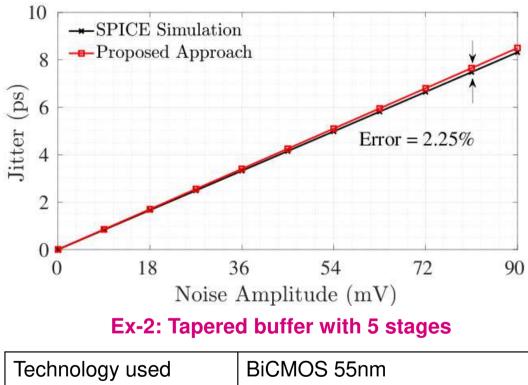

#### **Results**

life.augmented

| Technology used | BiCMOS 55nm<br>(STMicroelectronics) |

|-----------------|-------------------------------------|

| Supply voltage  | 1.8 V                               |

| Input data rate | 2 Gbps                              |

### **Results**

| Example   | Approach     | <b>CPU Time</b>  | Speed-up |

|-----------|--------------|------------------|----------|

| Example-1 | Conventional | 8 min. 34 sec.   | ~123     |

|           | Proposed     | <b>4.17 sec.</b> |          |

| Example-2 | Conventional | 12 min. 5 sec.   | ~133     |

|           | Proposed     | 5.44 sec.        |          |

#### Summary/Conclusion

- Faster estimation for PSIJ is required to reduced design cycle of SoCs.

- Semi-analytical methods can be useful for the same.

- Effects of off-chip and on-chip interconnects on jitter should be studied thoroughly to avoid the complications in meeting the specifications of overall timing uncertainty!

## Thank You.